AVR32

32-bit Microcontrollers and Application Processors

Working with Bits and Bytes February 2009

Everywhere You Are®

# **Logic Instructions and Programs**

#### **READING**

#### The AVR Microcontroller and Embedded Systems using Assembly and C)

by Muhammad Ali Mazidi, Sarmad Naimi, and Sepehr Naimi

Chapter 5: Arithmetic, Logic Instructions, and Programs<sup>1</sup>

Section 5.3: Logic and Compare Instructions

Section 5.4: Rotate and Shift Instructions and Data Serialization

Section 5.5: BCD and ASCII Conversion

<sup>&</sup>lt;sup>1</sup> Sections 5.1 and 5.2 covered in AVR ALU and SREG Lecture

# **Contents**

| Reading                                                         | 2  |

|-----------------------------------------------------------------|----|

| Overview                                                        | 4  |

| Sample Application – Knight Rider                               | 5  |

| Sample Application – Bicycle Light                              |    |

| Clearing and Setting Bits                                       |    |

| Clearing and Setting a Bit in the AVR Status Register           |    |

| Testing Bits                                                    |    |

| Toggling Bits                                                   |    |

| Rotating and Shifting Bits                                      |    |

| Clearing and Setting a Bit in One of the first 32 I/O registers | 13 |

| Setting a Bit Pattern                                           | 14 |

| Questions                                                       | 15 |

| Appendix A: Knight Rider Optimized                              | 16 |

| Appendix B: Knight Rider Addressing Indirect                    | 17 |

# **O**VERVIEW

## Clearing and Setting a Bit In ...

| Where                         | Instruction         | Alternative | Notes                                 |

|-------------------------------|---------------------|-------------|---------------------------------------|

| I/O (0 – 31)                  | cbi, sbi            |             | Use with I/O Ports                    |

| SREG                          | cl{i,t,h,s,v,n,z,c} | bclr        |                                       |

|                               | se{i,t,h,s,v,n,z,c} | bset        |                                       |

| Working with General Purpose  | Register Bits       |             |                                       |

| Clearing and Setting a Byte   | clr, ser            |             |                                       |

| Clearing Bits                 | and, cbr            | andi        |                                       |

| Testing Bits                  | and                 |             | Also consider using sbrc, sbrs, sbic, |

|                               |                     |             | sbis (see Control Transfer Lecture)   |

| Testing a Bit                 | bst ⇒brts, brtc     |             |                                       |

| Testing a Byte                | tst ⇒breq, brne     |             |                                       |

| Setting Bits                  | or, sbr             | ori         |                                       |

| Inserting a Bit Pattern       | cbr → sbr           | and → or    |                                       |

| Complementing (Toggling) Bits | eor                 |             |                                       |

| Rotating Bits                 | rol, ror            |             |                                       |

| Shifting Bits                 | lsl, lsr, asr       |             |                                       |

| Swapping Nibbles              | swap                |             |                                       |

### SAMPLE APPLICATION - KNIGHT RIDER

#### KnightRider:

```

; See page 5 and 6 - Clearing and Setting Bits

clr r16 // start with r9 bit 6 set - LED 6

r16, 0b10000000

sbr

; Q1: How could we have done this using 1 instruction?

ldi

r17, (1<<SREG T) // equivalent to 0b01000000

; See page 7 - Clearing and Setting a Bit in the AVR

Status Register

// initialize T = 0, scan right

clt

; See page 8 - Testing Bits

loop:

r19, 0b100000001

ldi

r19,r16 // test if LED hit is at an edge

and

contScan // continue scan if z = 0

breq

; See page 9 - Toggling Bits

r16, SREG // toggle T bit

in

r16, r17

eor

out

SREG, r16

; See page 10 - Rotating and Shifting Bits

contScan:

scanLeft // rotate right or left

brts

lsr

r16

rjmp

cont

scanLeft:

lsl

r16

cont:

spiLEDS, r16

mov

call WriteDisplay

rcall Delay

rjmp

loop

```

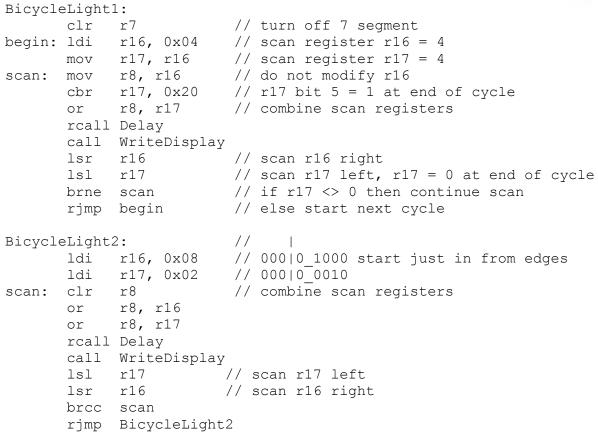

#### SAMPLE APPLICATION — BICYCLE LIGHT

A bicycle light has 5 LEDs.

BicycleLight1: A repeating pattern starts with the center LED turned ON. The center LED is then turned OFF, and the LEDs to the left and right of the center LED are turned ON. Each LED continues its scan to the left or right. Once the LEDs reach the end the pattern repeats itself. Using the CSULB shield, write a program to simulate this bicycle light.

BicycleLight2: Same as Bicycle1 except when LEDs reach the edge, they scan back to the center.

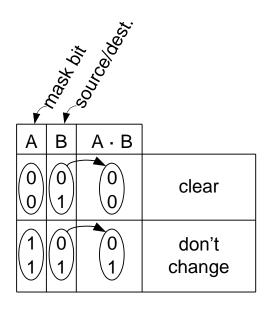

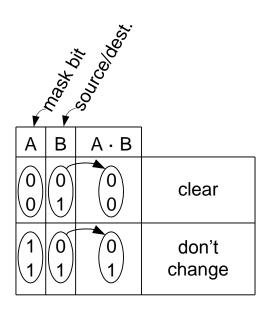

## **CLEARING AND SETTING BITS**

## To clear a bit set the corresponding mask bit to 0

```

and source/dest register, mask register

```

Problem: Convert numeric ASCII value ('0' - '9') to its binary coded decimal (BCD) equivalent (0-9).

- What we have: '0' to '9' which equals 30<sub>16</sub> to 39<sub>16</sub>

- What we want: 0 to 9 which equals  $00_{16}$  to  $09_{16}$

#### Solution: Mask out high-order nibble

```

lds r16, ascii_value

ldi r17, 0x0F

and r16, r17 // or simply andi

sts bcd_value, r16

```

## An alternative to the and instruction is the Clear Bits in Register cbr instruction.

```

cbr source/dest register, mask bits

```

The cbr instruction clears the specified bits in the source/Destination Register (Rd). It performs the logical AND between the contents of register Rd and the complement of the constant mask (K). The result will be placed in register Rd.

$Rd \leftarrow Rd \cdot (0xFF - K)$ , here is how the previous problem would be solved using the cbr instruction.

```

lds r16, ascii_value

cbr r16, 0xF0

sts bcd value, r16

```

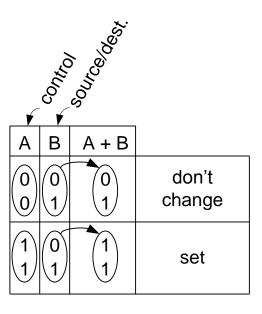

## Clearing and **Setting** Bits

## To set a bit set the corresponding mask bit to 0

```

or source/dest register, control register

```

#### Example: Set to one (1) bits 4 and 2 in some port.

#### An alternative to the or instruction is the Set Bits in Register sbr instruction.

```

sbr source/dest register, mask bits

```

The sbr instruction sets the specified bits in the source/Destination Register (Rd). It performs the logical ORI between the contents of register Rd and the constant control (K). The result will be placed in register Rd.

$$Rd \leftarrow Rd + K$$

Here is how the previous problem would be solved using the cbr instruction.

```

in     r16, some_port

sbr     r16, 0b00010100

out     some port, r16

```

## CLEARING AND SETTING A BIT IN THE AVR STATUS REGISTER<sup>2</sup>

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _    |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| 0x3F (0x5F)   | I   | T   | Н   | S   | V   | N   | Z   | С   | SREG |

| Read/Write    | R/W | •    |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

## **AVR Instructions for Clearing and Setting SREG bits**

## **Examples:**

#### **Disable all Interrupts**

cli

#### Set T bit

set

<sup>&</sup>lt;sup>2</sup> Source: ATmega328P Data Sheet <a href="http://www.atmel.com/dyn/resources/prod\_documents/81615.pdf">http://www.atmel.com/dyn/resources/prod\_documents/81615.pdf</a> Section 6.3 Status Register

#### **TESTING BITS**

#### Use the andi instruction to test if more than one bit is set

```

source/dest register, mask bits

andi

Example 1: Branch if bit 7 or bit 0 is set

// 7654 3210

r16, some bits // 1000 0000 ← example

lds

r16, 0b10000001

// 1000 0001

andi

brbc SREG Z, bit set

// 1000 0000 (alt. brne)

Example 2: Branch if bit 4 and bit 2 are clear

// 7654 3210

r16, some bits // 1101 1001 ← example

lds

r16, 0b00010100

// 0001 0100

andi

brbs SREG Z, bits zero // 0001 0000 (alt. breq)

```

Consider using one of the "Skip if Bit" instructions if you only need to test one bit.

Review "Control Transfer" lecture material for details.

## Use the tst instructions to test if a register is Zero or Minus.

Tests if a register is zero or negative. Performs a logical AND between a register and itself. The register will remain unchanged.

## **Example:** Branch if bear is in the forest

```

rcall inForest // returns false(r24 = 0) if bear is not in the forest tst r24 breq not in forest // branch if r24 = 0

```

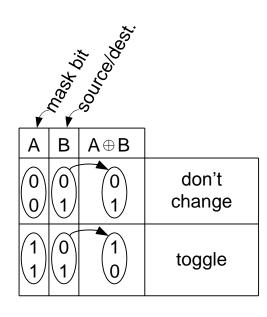

#### **TOGGLING BITS**

## To toggle (complement) a bit set the corresponding mask bit to 1

```

eor source/dest register, mask register

```

#### Example: Toggle bits 5 and 3 of I/O-Port D.

```

// 7654 3210

in r16, PORTD // 1101 1001 \leftarrow example

ldi r17, 0x28 // 0010 1000

eor r16, r17 // 1111 0001

out PORTD, r16

```

When toggling an I/O-Port bit, consider writing a one to the corresponding pin.

Review "AVR Peripherals" lecture material for details.

Example: Toggle bits 5 and 3 of I/O-Port D.

```

sbi PIND, PIND5 // equivalent to sbi 0x09, 5 sbi PIND, PIND3

```

When toggling a byte (8 bits), use the Complement instruction.

#### **Example: Write TurnAround code snip-it (i.e., toggle SRAM variable dir)**

```

// 7654 3210

lds r16, dir // 1101 1001 ← facing East

com r16 // 0010 0110 ← facing West

cbr r16, 0xFC // 1111 1100 clear unused bits (optional)

sts dir, r16 // 0000 0010

```

Question: How could you have complemented dir without modifying the other 6 bits?

#### **ROTATING AND SHIFTING BITS**

Rotate Instructions allow us to rearrange bits without losing information and to sequentially test bit (brcc, brcs). Shift instructions allow us to quickly multiply and/or divide signed and/or unsigned numbers by 2.

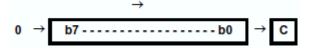

## **Rotate Left through Carry**

rol Rd

Shifts all bits in Rd one place to the left. The C Flag is shifted into bit 0 of Rd. Bit 7 is shifted into the C Flag. This operation, combined with LSL, effectively multiplies multi-byte signed and unsigned values by two.

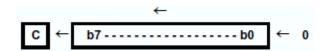

#### **Rotate Right through Carry**

ror Rd

Shifts all bits in Rd one place to the right. The C Flag is shifted into bit 7 of Rd. Bit 0 is shifted into the C Flag. This operation, combined with ASR, effectively divides multi-byte signed values by two. Combined with LSR it effectively divides multibyte unsigned values by two. The Carry Flag can be used to round the result.

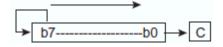

#### **Logical Shift Left (Arithmetic Shift Left)**

lsl Rd

Shifts all bits in Rd one place to the left. Bit 0 is cleared. Bit 7 is loaded into the C Flag of the SREG. This operation effectively <u>multiplies signed and unsigned</u> <u>values by two</u>.

#### **Logical Shift Right**

lsr Rd

Shifts all bits in Rd one place to the right. Bit 7 is cleared. Bit 0 is loaded into the C Flag of the SREG. This operation effectively <u>divides an unsigned value by two</u>. The C Flag can be used to round the result.

#### **Arithmetic Shift Right**

asr Rd

Shifts all bits in Rd one place to the right. Bit 7 is held constant. Bit 0 is loaded into the C Flag of the SREG. This operation effectively <u>divides a signed value by two</u> without changing its sign. The Carry Flag can be used to round the result.

# CLEARING AND SETTING A BIT IN ONE OF THE FIRST 32 I/O REGISTERS

Example: Pulse Clock input of Proto-Shield Debounce D Flip-flop (PORTD5). Assume currently at logic 0.

sbi PORTD, 5 cbi PORTD, 5

| Address     | Name     | Bit 7            | Bit 6                          | Bit 5         | Bit 4            | Bit 3           | Bit 2  | Bit 1  | Bit 0  | Page   |

|-------------|----------|------------------|--------------------------------|---------------|------------------|-----------------|--------|--------|--------|--------|

| 0x1F (0x3F) | EECR     | -                | -                              | EEPM1         | EEPMO            | EERIE           | EEMPE  | EEPE   | EERE   | 21     |

| 0x1E (0x3E) | GPIOR0   | Va .             | General Purpose I/O Register 0 |               |                  |                 |        |        |        |        |

| 0x1D (0x3D) | EIMSK    |                  | -                              | -             | -                | _               | -      | INT1   | INTO   | 72     |

| 0x1C (0x3C) | EIFR     | -                | _                              | _             | _                |                 | _      | INTF1  | INTF0  | 72     |

| 0x1B (0x3B) | PCIFR    | 3 <del></del>    |                                | s <del></del> | -                | <del></del> :   | PCIF2  | PCIF1  | PCIF0  |        |

| 0x1A (0x3A) | Reserved | -                | -                              | -             | -                | -               | =      | -      | -      |        |

| 0x19 (0x39) | Reserved | · <del>···</del> | -                              | -             | -                | =               | -      | -      | -      |        |

| 0x18 (0x38) | Reserved | -                | -                              | -             | -                | _               | -      | -      | -      |        |

| 0x17 (0x37) | TIFR2    | / <del>-</del>   | -                              | -             | -                | _               | OCF2B  | OCF2A  | TOV2   | 163    |

| 0x16 (0x36) | TIFR1    | 1 <del>2-</del>  | -                              | ICF1          | -                | -               | OCF1B  | OCF1A  | TOV1   | 139    |

| 0x15 (0x35) | TIFRO    | 32               | 12-1                           | _             |                  | ( <u></u> )     | OCF0B  | OCF0A  | TOV0   |        |

| 0x14 (0x34) | Reserved |                  | =                              | -             | =                | =               | =      | =      | = "    |        |

| 0x13 (0x33) | Reserved | _                |                                | =             | 1 <del></del> .  |                 | -      |        | -      |        |

| 0x12 (0x32) | Reserved |                  | -                              |               | -                | : <del></del> : | -      | -      | -      |        |

| 0x11 (0x31) | Reserved | 2 <del></del>    | -                              | -             | : <del>-</del> : | -               | -      | -      | -      |        |

| 0x10 (0x30) | Reserved | -                | -                              |               | -                | -               | -      | -      | -      |        |

| 0x0F (0x2F) | Reserved | /=               | -                              | _             | -                | -               | -      | -      | -      |        |

| 0x0E (0x2E) | Reserved | -                | _                              | -             | -                | _               | _      | _      | _      |        |

| 0x0D (0x2D) | Reserved |                  |                                | _             |                  |                 | 1221   | 122    | _      |        |

| 0x0C (0x2C) | Reserved |                  | _                              | -             | _                | _               | _      | =      | =      |        |

| 0x0B (0x2B) | PORTD    | PORTD7           | PORTD6                         | PORTD5        | PORTD4           | PORTD3          | PORTD2 | PORTD1 | PORTD0 | 93     |

| 0x0A (0x2A) | DDRD     | DDD7             | DDD6                           | DDD5          | DDD4             | DDD3            | DDD2   | DDD1   | DDD0   | 93     |

| 0x09 (0x29) | PIND     | PIND7            | PIND6                          | PIND5         | PIND4            | PIND3           | PIND2  | PIND1  | PINDO  | 93     |

| 0x08 (0x28) | PORTC    | \$ <del></del>   | PORTC6                         | PORTC5        | PORTC4           | PORTC3          | PORTC2 | PORTC1 | PORTC0 | 92     |

| 0x07 (0x27) | DDRC     | -                | DDC6                           | DDC5          | DDC4             | DDC3            | DDC2   | DDC1   | DDC0   | 92     |

| 0x06 (0x26) | PINC     | -                | PINC6                          | PINC5         | PINC4            | PINC3           | PINC2  | PINC1  | PINC0  | 92     |

| 0x05 (0x25) | PORTB    | PORTB7           | PORTB6                         | PORTB5        | PORTB4           | PORTB3          | PORTB2 | PORTB1 | PORTB0 | 92     |

| 0x04 (0x24) | DDRB     | DDB7             | DDB6                           | DDB5          | DDB4             | DDB3            | DDB2   | DDB1   | DDB0   | 92     |

| 0x03 (0x23) | PINB     | PINB7            | PINB6                          | PINB5         | PINB4            | PINB3           | PINB2  | PINB1  | PINB0  | 92     |

| 0x02 (0x22) | Reserved | _                | -                              | -             | _                | _               | _      | _      | -      | 2000-5 |

| 0x01 (0x21) | Reserved | 8 <del></del>    | _                              | _             | _                | <del>-</del>    | -      | _      | _      |        |

| 0x0 (0x20)  | Reserved | _                | _                              | _             | _                | _               | _      | _      | _      |        |

### **SETTING A BIT PATTERN**

Use the Clear Bits in Register cbr or functionally equivalent andi instruction in combination with the Set Bits in Register sbr to set a bit pattern in a register.

Problem: Convert a binary coded decimal (BCD) (0-9) number to its ASCII equivalent value ('0'-'9').

- What we have: 0 to 9 which equals X0<sub>16</sub> to X9<sub>16</sub>

The X indicates that we do not know what is contained in this nibble.

- What we want: '0' to '9' which equals 30<sub>16</sub> to 39<sub>16</sub>

#### Solution: Set high-order nibble to 3<sub>16</sub>

#### What is Happening

## **QUESTIONS**

- 1. What instruction is used to divide a signed number by 2?

- 2. What instruction is used to multiply an unsigned number by 2?

- 3. What instruction(s) would be used to convert a word pointer into a byte pointer? A word pointer is a register pair like Z containing the address of a 16-bit data (2 byte) word in an SRAM Table. A byte pointer is a register pair like Z containing the address of an 8-bit data byte in a corresponding SRAM Table. Assuming there is a one-to-one relationship between each word in the first table with a byte in the second table. And remembering that SRAM is always addressed at the Byte level, how would convert a pointer defined for the word table into a pointer defined for the byte table.

#### APPENDIX A: KNIGHT RIDER OPTIMIZED

```

.INCLUDE <m328pdef.inc>

rjmp reset

.INCLUDE "spi shield.inc"

reset:

call InitShield

// initialize knight rider

ldi r16, 0b10000000 // start with r9 bit 7 set - LED 7

mov spiLEDS, r16

// initialize roulette

ldi r19,0xE0

ldi r20,0x1F

ldi r16,0x01

mov spi7SEG, r16

loop:

// night rider routine

ldi r16, 0b10000001

and r16, spiLEDS

// test if LED hit is at an edge

breq contScan

// continue scan if z = 0

bst spiLEDS, 0 // if right LED ON, then T = 1

contScan:

brts scanLeft

// rotate right or left

lsr spiLEDS

rjmp cont

scanLeft:

lsl spiLEDS

cont:

// roulette routine

add spi7SEG, r19

and spi7SEG, r20

rol spi7SEG

rcall WriteDisplay

rcall Delay

// display routine

rcall WriteDisplay

rcall Delay

rjmp loop

```

#### APPENDIX B: KNIGHT RIDER ADDRESSING INDIRECT

```

begin:

// loop 14 times

ldi r16, 14

ldi ZH, high(Table<<1) // set base address</pre>

ldi ZL, low(Table<<1)

scan:

// load constant to LED display register

lpm r9, Z+

rcall WriteDisplay // display routine

rcall Delay

dec r16

brne scan

// if r17 <> 0 then continue scan

rjmp begin

// else start next cycle

KnightRider: .DB 0x80, 0x40, 0x20, 0x10, 0x08, 0x04, 0x02

.DB 0x01, 0x02, 0x04, 0x08, 0x10, 0x20, 0x40

```