AVR® 8-bit Microcontrollers

AVR<sup>3</sup>2 32-bit Microcontrollers and Application Processors

**Addressing Modes** February 2009

Everywhere You Are®

# Addressing Modes Part I – Working with AVR's Load-Store RISC Architecure

### READING

The AVR Microcontroller and Embedded Systems using Assembly and C)

by Muhammad Ali Mazidi, Sarmad Naimi, and Sepehr Naimi

Chapter 2: AVR Architecture and Assembly Language Programming

Section 2.3: Using Instructions with the Data Memory

Chapter 6: AVR Advanced Assembly Language Programming

Section 6.2: Register and Direct Addressing Modes

# TABLE OF CONTENTS

| Load-Store Instructions and the ATmega328P Memory Model |

|---------------------------------------------------------|

| Load-Store Instructions and Addressing Modes            |

| Immediate                                               |

| Direct                                                  |

| Register-register Instructions                          |

| Register Direct                                         |

| Load-Store Program Example                              |

| Special Topic – Harvard versus Princeton Architecture   |

| Appendix A – ATmega328P Instruction Set                 |

# LOAD-STORE INSTRUCTIONS AND THE ATMEGA328P MEMORY MODEL

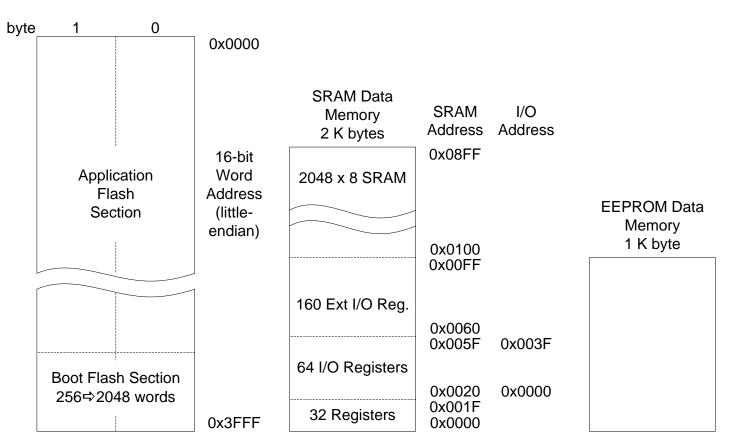

When selecting an addressing mode you should ask yourself where is the operand (data) located within the memory model of the AVR processor and when do I know its address (assembly time or at run time)<sup>1</sup>.

> FLASH Program Memory 16K x 16 (32 K bytes)

<sup>&</sup>lt;sup>1</sup> <u>http://www.atmel.com/dyn/resources/prod\_documents/doc0856.pdf</u> 8-bit AVR Instruction Set

# LOAD-STORE INSTRUCTIONS AND ADDRESSING MODES

- When loading and storing data we have several ways to "address" the data.

- The AVR microcontroller supports addressing modes for access to the Program memory (Flash) and Data memory (SRAM, Register file, I/O Memory, and Extended I/O Memory).

| Addressing Mode       Flash Program       SRAM Data       I/C         Immediate       ldi | 0   |

|-------------------------------------------------------------------------------------------|-----|

| Direct lds, sts in,                                                                       |     |

|                                                                                           |     |

| Indirect Ipm, spm (1) Id, st (2)                                                          | out |

|                                                                                           |     |

| lirect with Displacement Idd, std (3)                                                     |     |

|                                                                                           |     |

#### IMMEDIATE

Data is encoded with the instruction. Operand is therefore located in Flash Program Memory. This is why technically our memory model is a *Modified* Harvard.

ldi r16, 0x23 // where ldi = 1110, Rd = 0000<sub>2</sub>, and constant K = 00100011<sub>2</sub>

| 1110 KKKK | dddd | KKKK |

|-----------|------|------|

|-----------|------|------|

• Notice that only four bits (dddd) are set aside for defining destination register Rd. This limits us to  $2^4 = 16$  registers. The designers of the AVR processor chose registers 16 to 31 to be these registers (i.e.,  $16 \le \text{Rd} \le 31$ ).

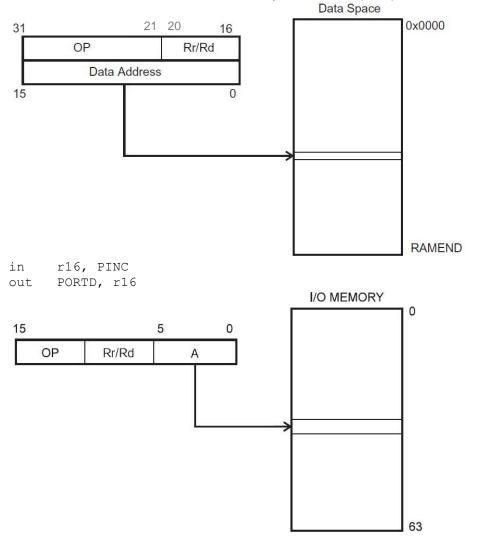

### DIRECT

lds r16, A sts A, r16

Within the AVR family there are two (2) possible lds/sts instructions. A specific family member will have only one lds/sts combination. The ATmega328P lds/sts instruction is illustrated here with the exception that 5 bits (not 4) encode Rr/Rd. This means all 32 registers are available to the lds/sts instruction.

# **REGISTER-REGISTER INSTRUCTIONS**

### Data Transfer

• Register-register move byte (mov) or word (movw)

#### Arithmetic and Logic (ALU)

- Two's complement negate (neg), Arithmetic add (add, adc, adiw), subtract (sub, subi, sbc, sbci), and multiply (mul, muls, mulsu, fmul, fmuls, fmulsu)

- Logical not (com), and (and, andi, cbr, tst), or (or, ori, sbr), exclusive or (eor)

- Clear (clr), set (ser), increment (inc), decrement (dec)

### Bit and Bit-Test

- Register logical shift left (lsl) or right(lsr); arithmetic shift right (asr); and rotate left or right (rol, ror)

- Register swap nibble (swap)

- Register bit load (bld) or store (bst) from/to T flag in the Status Register SREG

- I/O Register Clear (cbi) or set (sbi) a bit

- Clear (clFlag) or set (seFlag) a Flag bit in the Status Register SREG by name (I, T, H, S, V, N, Z, C) or bit (bclr, bset).

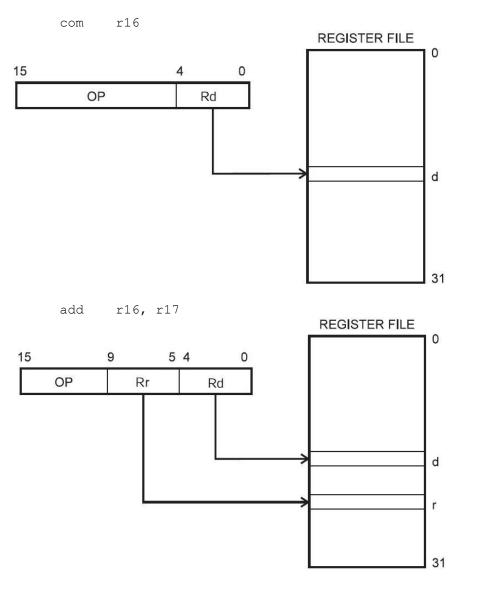

# **REGISTER DIRECT**

In the following figures, OP means the operation code part of the instruction word. To simplify, not all figures show the exact location of the addressing bits. To generalize, the abstract terms RAMEND and FLASHEND have been used to represent the highest location in data and program space.

## LOAD-STORE PROGRAM EXAMPLE

# Write an Assembly program to add two 8-bit numbers.

$\boldsymbol{C}=\boldsymbol{A}+\boldsymbol{B}$

| lds | r16, A   | ; | 1. | Load variables |

|-----|----------|---|----|----------------|

| lds | r17, B   |   |    |                |

| add | r16, r17 | ; | 2. | Do something   |

| sts | C, r16   | ; | 3. | Store answer   |

- Identify the operation, source operand, destination operand in the first *Data Transfer* instruction.

- Identify the source/destination operand in the *Arithmetic and Logic* (ALU) instruction.

- What addressing mode is used by the source operand, in the first instruction?

- Show contents of Flash Program Memory (mnemonics)

- Show contents of SRAM Data Memory, assuming variables are stored in sequential memory locations starting at address 0100<sub>16</sub>.

- Modify the program to leave register r16 unchanged by making a copy (use r15).

## SPECIAL TOPIC – HARVARD VERSUS PRINCETON ARCHITECTURE

#### Princeton or Von Neumann Memory Model

Program and data share the same memory space. Processors used in all personal computers, like the Pentium, implement a von Neumann architecture.

#### Harvard Memory Model

Program and data memory are separated. The AVR processors among others including the Intel 8051 use this memory model. One advantage of the Harvard architecture for microcontrollers is that program memory can be wider than data memory. This allows the processor to implement more instructions while still working with 8-bit data. For the AVR processor program memory is 16-bits wide while data memory is only 8-bits.

You may have already noticed that when you single step your program in the simulator of AVR Studio it is incremented by 1 each time an instruction is executed. No surprise there right? Wrong. The program memory of the AVR processor can also be accessed at the byte level. In most cases this apparent paradox is transparent to the operation of your program with one important exception. When you want to access data stored in program memory, you will be working with byte addresses not words (16-bits). The assembler is not smart enough to know the difference and so when you ask for an address in program memory it returns its word address. To convert this word address into a byte address you need to multiply it by 2. Problematically we do this by using the shift left syntax of C++ to explicitly tell the assembler to multiply the word address by 2. Remember, when you shift left one place you are effectively multiplying by 2.

With this in mind, we would interpret the following AVR instruction as telling the AVR assembler to convert the word address of label beehives in program memory to a byte address and then to take the low order of the resulting value and put into the source operand of the instruction.

ldi ZL,low(beeHives<<1) // load word address of beeHives look-up</pre>

# APPENDIX A – ATMEGA328P INSTRUCTION SET<sup>2</sup>

| Mnemonics            | Operands          | Description                                                               | Operation                                                                                                                                          | Flags              | #Clocks |

|----------------------|-------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------|

| ARITHMETIC AND       | LOGIC INSTRUCTION | s                                                                         |                                                                                                                                                    |                    |         |

| ADD                  | Rd, Rr            | Add two Registers                                                         | Rd ← Rd + Rr                                                                                                                                       | Z.C.N.V.H          | 1       |

| ADC                  | Rd, Rr            | Add with Carry two Registers                                              | $Rd \leftarrow Rd + Rr + C$                                                                                                                        | Z,C,N,V,H          | 1       |

| ADIW                 | Rdl,K             | Add Immediate to Word                                                     | Rdh:RdI ← Rdh:RdI + K                                                                                                                              | Z,C,N,V,S          | 2       |

| SUB                  | Rd, Rr            | Subtract two Registers                                                    | Rd ← Rd - Rr                                                                                                                                       | Z,C,N,V,H          | 1       |

| SUBI                 | Rd, K             | Subtract Constant from Register                                           | Rd ← Rd - K                                                                                                                                        | Z,C,N,V,H          | 1       |

| SBC                  | Rd, Rr            | Subtract with Carry two Registers                                         | Rd ← Rd - Rr - C                                                                                                                                   | Z,C,N,V,H          | 1       |

| SBCI                 | Rd, K             | Subtract with Carry Constant from Reg.                                    | Rd ← Rd - K - C                                                                                                                                    | Z,C,N,V,H          | 1       |

| SBIW                 | RdI,K             | Subtract Immediate from Word                                              | Rdh:RdI ← Rdh:RdI - K                                                                                                                              | Z,C,N,V,S          | 2       |

| AND                  | Rd, Rr            | Logical AND Registers                                                     | Rd ← Rd • Rr                                                                                                                                       | Z,N,V              | 1       |

| ANDI                 | Rd, K             | Logical AND Register and Constant                                         | Rd ← Rd • K                                                                                                                                        | Z,N,V              | 1       |

| OR                   | Rd, Rr            | Logical OR Registers                                                      | Rd ← Rd v Rr                                                                                                                                       | Z,N,V              | 1       |

| ORI                  | Rd, K             | Logical OR Register and Constant                                          | Rd ← Rd v K                                                                                                                                        | Z,N,V              | 1       |

| EOR                  | Rd, Rr            | Exclusive OR Registers                                                    | Rd ← Rd ⊕ Rr                                                                                                                                       | Z,N,V              | 1       |

| COM                  | Rd                | One's Complement                                                          | Rd ← 0xFF – Rd                                                                                                                                     | Z,C,N,V            | 1       |

| NEG                  | Rd                | Two's Complement                                                          | Rd ← 0x00 - Rd                                                                                                                                     | Z.C.N.V.H          | 1       |

| SBR                  | Rd,K              | Set Bit(s) in Register                                                    | Rd ← Rd v K                                                                                                                                        | Z,N,V              | 1       |

| CBR                  | Rd,K              | Clear Bit(s) in Register                                                  | $Rd \leftarrow Rd \bullet (0xFF - K)$                                                                                                              | Z,N,V              | 1       |

| INC                  | Rd                | Increment                                                                 | Rd ← Rd + 1                                                                                                                                        | Z,N,V              | 1       |

| DEC                  | Rd                | Decrement                                                                 | Rd ← Rd – 1                                                                                                                                        | Z,N,V              | 1       |

| TST                  | Rd                | Test for Zero or Minus                                                    | Rd ← Rd • Rd                                                                                                                                       | Z,N,V              | 1       |

| CLR                  | Rd                | Clear Register                                                            | Rd ← Rd ⊕ Rd                                                                                                                                       | Z,N,V              | 1       |

| SER                  | Rd                | Set Register                                                              | Rd ← 0xFF                                                                                                                                          | None               | 1       |

| MUL                  | Rd, Rr            | Multiply Unsigned                                                         | R1:R0 ← Rd x Rr                                                                                                                                    | Z.C                | 2       |

| MULS                 | Rd, Rr            | Multiply Signed                                                           | R1:R0 ← Rd x Rr                                                                                                                                    | Z,C                | 2       |

| MULSU                | Rd, Rr            | Multiply Signed with Unsigned                                             | B1:B0 ← Bd x Br                                                                                                                                    | Z.C                | 2       |

| FMUL                 | Rd, Rr            | Fractional Multiply Unsigned                                              | B1:B0 ← (Bd x Br) << 1                                                                                                                             | Z,C                | 2       |

| FMULS                | Rd, Rr            | Fractional Multiply Signed                                                | $B1:B0 \leftarrow (Bd \times Br) << 1$                                                                                                             | Z.C                | 2       |

| FMULSU               | Bd, Br            | Fractional Multiply Signed with Unsigned                                  | $R1:R0 \leftarrow (Rd \times Rr) << 1$                                                                                                             | Z.C                | 2       |

| BRANCH INSTRUC       |                   |                                                                           |                                                                                                                                                    |                    | _       |

| BJMP                 | k                 | Relative Jump                                                             | $PC \leftarrow PC + k + 1$                                                                                                                         | None               | 2       |

| IJMP                 |                   | Indirect Jump to (Z)                                                      | PC ← Z                                                                                                                                             | None               | 2       |

| JMP <sup>(1)</sup>   | k                 | Direct Jump                                                               | PC ← k                                                                                                                                             | None               | 3       |

| RCALL                | k                 | Relative Subroutine Call                                                  | $PC \leftarrow PC + k + 1$                                                                                                                         | None               | 3       |

| ICALL                |                   | Indirect Call to (Z)                                                      | PC ← Z                                                                                                                                             | None               | 3       |

| CALL <sup>(1)</sup>  | k                 | Direct Subroutine Call                                                    | PC ← k                                                                                                                                             | None               | 4       |

| RET                  | <u> </u>          | Subroutine Return                                                         | PC ← STACK                                                                                                                                         | None               | 4       |

| RETI                 |                   | Interrupt Return                                                          | PC ← STACK                                                                                                                                         | l                  | 4       |

| CPSE                 | Rd,Rr             | Compare, Skip if Equal                                                    | if (Rd = Rr) PC $\leftarrow$ PC + 2 or 3                                                                                                           | None               | 1/2/3   |

| CP                   | Rd,Br             | Compare                                                                   | Rd - Rr                                                                                                                                            | Z. N.V.C.H         | 1       |

| CPC                  | Rd,Rr             | Compare with Carry                                                        | Rd – Rr – C                                                                                                                                        | Z, N,V,C,H         | 1       |

| CPI                  | Rd,K              | Compare Register with Immediate                                           | Rd - K                                                                                                                                             | Z, N,V,C,H         | 1       |

| SBRC                 | Br, b             | Skip if Bit in Register Cleared                                           | if $(\text{Br}(b)=0) \text{ PC} \leftarrow \text{PC} + 2 \text{ or } 3$                                                                            | Z, N,V,C,H<br>None | 1/2/3   |

| SBRS                 | Br, b             | Skip if Bit in Register cleared                                           | if $(\text{Rr}(b)=0) \text{ PC} \leftarrow \text{PC} + 2 \text{ or } 3$<br>if $(\text{Rr}(b)=1) \text{ PC} \leftarrow \text{PC} + 2 \text{ or } 3$ | None               | 1/2/3   |

| SBIC                 | P, b              | Skip if Bit in I/O Register Cleared                                       | if $(P(b)=0) PC \leftarrow PC + 2 \text{ or } 3$<br>if $(P(b)=0) PC \leftarrow PC + 2 \text{ or } 3$                                               | None               | 1/2/3   |

| SBIS                 | P, b              | Skip if Bit in I/O Register Cleared<br>Skip if Bit in I/O Register is Set | if $(P(b)=0) PC \leftarrow PC + 2 \text{ or } 3$<br>if $(P(b)=1) PC \leftarrow PC + 2 \text{ or } 3$                                               | None               | 1/2/3   |

| BRBS                 | P, D<br>s, k      | Branch if Status Flag Set                                                 | if (SREG(s) = 1) then PC $\leftarrow$ PC + 2 or 3<br>if (SREG(s) = 1) then PC $\leftarrow$ PC+k + 1                                                | None               | 1/2/3   |

| BRBC                 | s, k              | Branch if Status Flag Set<br>Branch if Status Flag Cleared                | if (SREG(s) = 0) then PC+PC+k + 1<br>if (SREG(s) = 0) then PC+PC+k + 1                                                                             | None               | 1/2     |

| BREQ                 | s, K<br>k         | Branch if Status Flag Cleared<br>Branch if Equal                          | if (SHEG(s) = 0) then PC $\leftarrow$ PC+k + 1<br>if (Z = 1) then PC $\leftarrow$ PC + k + 1                                                       | None               | 1/2     |

| BRNE                 | к<br>k            | Branch if Equal<br>Branch if Not Equal                                    | if (Z = 1) then PC $\leftarrow$ PC + k + 1<br>if (Z = 0) then PC $\leftarrow$ PC + k + 1                                                           | None               | 1/2     |

| BRCS                 | к<br>k            | Branch if Carry Set                                                       | if ( $Z = 0$ ) then PC $\leftarrow$ PC + k + 1<br>if (C = 1) then PC $\leftarrow$ PC + k + 1                                                       | None               | 1/2     |

| BRCC                 | к<br>k            | Branch if Carry Set<br>Branch if Carry Cleared                            | if (C = 1) then $PC \leftarrow PC + k + 1$<br>if (C = 0) then $PC \leftarrow PC + k + 1$                                                           | None               | 1/2     |

| BRSH                 | к<br>k            |                                                                           | if (C = 0) then PC $\leftarrow$ PC + k + 1<br>if (C = 0) then PC $\leftarrow$ PC + k + 1                                                           | None               | 1/2     |

| BRLO                 | к<br>k            | Branch if Same or Higher<br>Branch if Lower                               | if (C = 0) then PC $\leftarrow$ PC + k + 1<br>if (C = 1) then PC $\leftarrow$ PC + k + 1                                                           | None               | 1/2     |

| BRMI                 |                   |                                                                           |                                                                                                                                                    |                    | 1/2     |

|                      | k                 | Branch if Minus                                                           | if $(N = 1)$ then PC $\leftarrow$ PC + k + 1                                                                                                       | None               |         |

| BRPL                 | k                 | Branch if Plus                                                            | if $(N = 0)$ then PC $\leftarrow$ PC + k + 1                                                                                                       | None               | 1/2     |

| BRGE                 | k                 | Branch if Greater or Equal, Signed                                        | if $(N \oplus V= 0)$ then PC $\leftarrow$ PC + k + 1                                                                                               | None               | 1/2     |

| BRLT                 | k                 | Branch if Less Than Zero, Signed                                          | if $(N \oplus V = 1)$ then PC $\leftarrow$ PC + k + 1                                                                                              | None               | 1/2     |

| BRHS                 | k                 | Branch if Half Carry Flag Set                                             | if (H = 1) then PC $\leftarrow$ PC + k + 1                                                                                                         | None               | 1/2     |

| BRHC                 | k                 | Branch if Half Carry Flag Cleared                                         | if (H = 0) then PC $\leftarrow$ PC + k + 1                                                                                                         | None               | 1/2     |

| BRTS                 | k                 | Branch if T Flag Set                                                      | if $(T = 1)$ then PC $\leftarrow$ PC + k + 1                                                                                                       | None               | 1/2     |

|                      | k                 | Branch if T Flag Cleared                                                  | if $(T = 0)$ then PC $\leftarrow$ PC + k + 1                                                                                                       | None               | 1/2     |

|                      |                   |                                                                           |                                                                                                                                                    |                    |         |

| BRTC<br>BRVS<br>BRVC | k                 | Branch if Overflow Flag is Set                                            | if (V = 1) then PC $\leftarrow$ PC + k + 1<br>if (V = 0) then PC $\leftarrow$ PC + k + 1                                                           | None               | 1/2     |

<sup>&</sup>lt;sup>2</sup> Source: ATmega328P Data Sheet <u>http://www.atmel.com/dyn/resources/prod\_documents/8161S.pdf</u> Chapter 31 Instruction Set Summary

| Mnemonics        | Operands     | Description                      | Operation                                                          | Flags   | #Clocks |

|------------------|--------------|----------------------------------|--------------------------------------------------------------------|---------|---------|

| BRIE             | k            | Branch if Interrupt Enabled      | if $(I = 1)$ then PC $\leftarrow$ PC + k + 1                       | None    | 1/2     |

| BRID             | k            | Branch if Interrupt Disabled     | if (1 = 0) then PC $\leftarrow$ PC + k + 1                         | None    | 1/2     |

| BIT AND BIT-TEST | INSTRUCTIONS |                                  |                                                                    |         |         |

| SBI              | P,b          | Set Bit in I/O Register          | I/O(P,b) ← 1                                                       | None    | 2       |

| CBI              | P,b          | Clear Bit in I/O Register        | I/O(P,b) ← 0                                                       | None    | 2       |

| LSL              | Rd           | Logical Shift Left               | $Rd(n+1) \leftarrow Rd(n), Rd(0) \leftarrow 0$                     | Z,C,N,V | 1       |

| LSR              | Rd           | Logical Shift Right              | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0$                     | Z,C,N,V | 1       |

| ROL              | Rd           | Rotate Left Through Carry        | $Rd(0) \leftarrow C, Rd(n+1) \leftarrow Rd(n), C \leftarrow Rd(7)$ | Z,C,N,V | 1       |

| ROR              | Rd           | Rotate Right Through Carry       | $Rd(7) \leftarrow C, Rd(n) \leftarrow Rd(n+1), C \leftarrow Rd(0)$ | Z,C,N,V | 1       |

| ASR              | Rd           | Arithmetic Shift Right           | Rd(n) ← Rd(n+1), n=06                                              | Z,C,N,V | 1       |

| SWAP             | Rd           | Swap Nibbles                     | Rd(30)←Rd(74),Rd(74)←Rd(30)                                        | None    | 1       |

| BSET             | 8            | Flag Set                         | SREG(s) ← 1                                                        | SREG(s) | 1       |

| BCLR             | s            | Flag Clear                       | SREG(s) ← 0                                                        | SREG(s) | 1       |

| BST              | Rr, b        | Bit Store from Register to T     | T ← Rr(b)                                                          | Т       | 1       |

| BLD              | Rd, b        | Bit load from T to Register      | Rd(b) ← T                                                          | None    | 1       |

| SEC              |              | Set Carry                        | C ← 1                                                              | С       | 1       |

| CLC              |              | Clear Carry                      | C ← 0                                                              | С       | 1       |

| SEN              |              | Set Negative Flag                | N ← 1                                                              | N       | 1       |

| CLN              |              | Clear Negative Flag              | N ← 0                                                              | N       | 1       |

| SEZ              |              | Set Zero Flag                    | Z ← 1                                                              | Z       | 1       |

| CLZ              |              | Clear Zero Flag                  | Z ← 0                                                              | Z       | 1       |

| SEI              |              | Global Interrupt Enable          | ← 1                                                                | 1       | 1       |

| CLI              |              | Global Interrupt Disable         | 1←0                                                                | 1       | 1       |

| SES              |              | Set Signed Test Flag             | S ← 1                                                              | S       | 1       |

| CLS              |              | Clear Signed Test Flag           | S ← 0                                                              | S       | 1       |

| SEV              |              | Set Twos Complement Overflow.    | V ← 1                                                              | V       | 1       |

| CLV              |              | Clear Twos Complement Overflow   | V ← 0                                                              | v       | 1       |

| SET              |              | Set T in SREG                    | T ← 1                                                              | T       | 1       |

| CLT              |              | Clear T in SREG                  | T ← 0                                                              | Т       | 1       |

| SEH              |              | Set Half Carry Flag in SREG      | H←1                                                                | н       | 1       |

| CLH              |              | Clear Half Carry Flag in SREG    | H←0                                                                | Н       | 1       |

| DATA TRANSFER I  |              |                                  |                                                                    | 1       | 1       |

| MOV              | Rd, Rr       | Move Between Registers           | Rd ← Rr                                                            | None    | 1       |

| MOVW             | Rd, Rr       | Copy Register Word               | Rd+1:Rd ← Rr+1:Rr                                                  | None    | 1       |

| LDI              | Rd, K        | Load Immediate                   | Rd ← K                                                             | None    | 1       |

| LD               | Rd, X        | Load Indirect                    | $Rd \leftarrow (X)$                                                | None    | 2       |

| LD               | Rd, X+       | Load Indirect and Post-Inc.      | $Rd \leftarrow (X), X \leftarrow X + 1$                            | None    | 2       |

| LD               | Rd, - X      | Load Indirect and Pre-Dec.       | $X \leftarrow X - 1, Rd \leftarrow (X)$                            | None    | 2       |

| LD               | Rd, Y        | Load Indirect                    | $Rd \leftarrow (Y)$                                                | None    | 2       |

| LD               | Rd, Y+       | Load Indirect and Post-Inc.      | $Rd \leftarrow (Y), Y \leftarrow Y + 1$                            | None    | 2       |

| LD               | Rd, - Y      | Load Indirect and Pre-Dec.       | $Y \leftarrow Y - 1, Rd \leftarrow (Y)$                            | None    | 2       |

| LDD              | Rd,Y+q       | Load Indirect with Displacement  | $Rd \leftarrow (Y + q)$                                            | None    | 2       |

| LD               | Rd, Z        | Load Indirect                    | Rd ← (Z)                                                           | None    | 2       |

| LD               | Rd, Z+       | Load Indirect and Post-Inc.      | $\operatorname{Rd} \leftarrow (Z), Z \leftarrow Z+1$               | None    | 2       |

| LD               | Rd, -Z       | Load Indirect and Pre-Dec.       | $Z \leftarrow Z - 1, Rd \leftarrow (Z)$                            | None    | 2       |

| LDD              | Rd, Z+q      | Load Indirect with Displacement  | $Rd \leftarrow (Z + q)$                                            | None    | 2       |

| LDS              | Rd, k        | Load Direct from SRAM            | $Rd \leftarrow (k)$                                                | None    | 2       |

| ST               | X, Br        | Store Indirect                   | (X) ← Rr                                                           | None    | -       |

| ST               | X+, Rr       | Store Indirect and Post-Inc.     | $(X) \leftarrow \operatorname{Rr}, X \leftarrow X + 1$             | None    | 2       |

| ST               | - X, Rr      | Store Indirect and Pre-Dec.      | $X \leftarrow X - 1, (X) \leftarrow Br$                            | None    | 2       |

| ST               | Y, Br        | Store Indirect                   | (Y) ← Br                                                           | None    |         |

| ST               | Y+, Br       | Store Indirect and Post-Inc.     | $(Y) \leftarrow Br, Y \leftarrow Y + 1$                            | None    | 2       |

| ST               | - Y, Rr      | Store Indirect and Pre-Dec.      | $Y \leftarrow Y - 1, (Y) \leftarrow Br$                            | None    | 2       |

| STD              | Y+q,Rr       | Store Indirect with Displacement | (Y + q) ← Rr                                                       | None    | 2       |

| ST               | Z, Rr        | Store Indirect                   | (Z) ← Br                                                           | None    | 2       |

| ST               | Z+, Rr       | Store Indirect and Post-Inc.     | $(Z) \leftarrow \operatorname{Rr}, Z \leftarrow Z + 1$             | None    | 2       |

| ST               | -Z, Rr       | Store Indirect and Pre-Dec.      | $Z \leftarrow Z - 1, (Z) \leftarrow Rr$                            | None    |         |

| STD              | Z+q,Rr       | Store Indirect with Displacement | (Z + q) ← Rr                                                       | None    | 2       |

| STS              | k, Rr        | Store Direct to SRAM             | (k) ← Rr                                                           | None    | 2       |

| LPM              |              | Load Program Memory              | R0 ← (Z)                                                           | None    | 3       |

| LPM              | Rd, Z        | Load Program Memory              | $Rd \leftarrow (Z)$                                                | None    | 3       |

| LPM              | Rd, Z+       | Load Program Memory and Post-Inc | $Rd \leftarrow (Z), Z \leftarrow Z+1$                              | None    | 3       |

| SPM              |              | Store Program Memory             | (Z) ← R1:R0                                                        | None    | -       |

| IN               | Rd, P        | In Port                          | Rd ← P                                                             | None    | 1       |

| OUT              | P, Br        | Out Port                         | P ← Br                                                             | None    | 1       |

| PUSH             | Br           | Push Register on Stack           | STACK ← Br                                                         | None    | 2       |

| Mnemonics                | Operands | Description             | Operation                                | Flags | #Clocks |  |  |  |

|--------------------------|----------|-------------------------|------------------------------------------|-------|---------|--|--|--|

| POP                      | Rd       | Pop Register from Stack | Rd ← STACK                               | None  | 2       |  |  |  |

| MCU CONTROL INSTRUCTIONS |          |                         |                                          |       |         |  |  |  |

| NOP                      |          | No Operation            |                                          | None  | 1       |  |  |  |

| SLEEP                    |          | Sleep                   | (see specific descr. for Sleep function) | None  | 1       |  |  |  |

| WDR                      |          | Watchdog Reset          | (see specific descr. for WDR/timer)      | None  | 1       |  |  |  |

| BREAK                    |          | Break                   | For On-chip Debug Only                   | None  | N/A     |  |  |  |

Note: 1. These instructions are only available in ATmega168PA and ATmega328P.